The automotive semiconductor landscape is rapidly evolving with the emergence of

centralized compute architectures, software-defined vehicles, and autonomous

driving platforms. These systems demand unprecedented levels of performance,

determinism, scalability, and functional safety. To meet these requirements, the

industry is increasingly moving away from monolithic SoCs toward chiplet-based

architectures, where heterogeneous processing elements are integrated using

standardized high-speed interconnects. The Universal Chiplet Interconnect

Express (UCIe) standard plays a pivotal role in enabling this transition.

Virtual component modelling of UCIe-based systems allows architects and software

teams to explore, validate, and optimize complex automotive SoCs well before

silicon availability. This blog discusses how UCIe cores are modeled for automotive

use cases, examines the layered architecture and protocol behavior, explains the

concept of flits, and highlights the relevance of virtual modeling tools, middleware,

SILkit, TLM-based integration, and the skill sets required for engineers entering this

domain.

UCIe Core Usage in Automotive Applications

Modern vehicles integrate multiple high-performance compute domains supporting

ADAS, autonomous driving, infotainment, gateway networking, and body electronics.

These domains require high-bandwidth communication between CPUs, AI

accelerators, vision processors, memory subsystems, and networking IPs, often

sourced from different vendors. UCIe enables this integration by providing a

standardized, low-latency, high-throughput chiplet interconnect that supports

interoperability and modular system design.

In automotive systems, UCIe is particularly relevant for centralized domain

controllers and zonal architectures where compute resources are distributed across

chiplets but must behave as a coherent system. Virtual modelling of UCIe cores

allows automotive OEMs and Tier-1 suppliers to validate latency, bandwidth,

determinism, and fault scenarios early, supporting safety analysis and compliance

with standards such as ISO 26262.

Layered Architecture of UCIe

The UCIe specification follows a layered architectural approach that separates

physical signaling concerns from protocol and transaction semantics. This separation

is crucial for modelling because it enables abstraction at different fidelity levels

depending on the use case.

At the lowest level, the physical layer defines signaling, lane configuration, clocking,

link training, and power management. While detailed PHY modeling is not always

required at the virtual prototype level, its behavior influences latency and error

handling assumptions.

Above the physical layer, the transport and link layers manage packetization,

reliability, ordering, and flow control. These layers are central to performance

modelling, especially in automotive systems where predictable behavior is critical.

The protocol layer defines how higher-level transactions are encapsulated and

transferred across the interconnect, while the transaction layer interfaces directly

with software-visible memory and I/O operations.

A layered modelling approach allows designers to selectively abstract lower layers

while retaining protocol accuracy where timing, ordering, or safety behavior must be

validated.

Most Used Protocol Layers in Automotive Modelling

In automotive-focused UCIe modelling, the transport and protocol layers receive the

most attention because they determine how transactions flow across chiplets under

varying traffic conditions. Memory-mapped transactions, cache-coherent accesses,

and streaming data flows are commonly modeled to reflect ADAS sensor pipelines

and AI workloads.

Automotive systems often require quality-of-service differentiation to ensure that

safety-critical traffic is prioritized over non-critical workloads. Virtual models of UCIe

protocol behavior help engineers study congestion scenarios, arbitration policies,

and back-pressure effects long before hardware is finalized.

Concept of Flits in UCIe

A fundamental concept in UCIe communication is the flit, or flow control unit. Flits

are the smallest units of data transfer used for managing flow control across the

interconnect. Larger packets are segmented into flits, enabling fine-grained control

over bandwidth usage and congestion handling.

From a modelling perspective, flit-based abstraction is extremely valuable. It allows

simulation of realistic traffic patterns, latency variations, and buffering behavior

without requiring full cycle-accurate PHY models. In automotive systems, where

deterministic latency paths are critical for safety functions, flit-level modeling helps

identify worst-case scenarios and ensures system robustness.

Relevance of UCIe Modelling in Chiplet-Based Designs

Chiplet-based architectures are becoming a cornerstone of automotive SoC design

due to their scalability, cost efficiency, and reuse potential. However, this modularity

introduces complexity in system integration, performance tuning, and safety

validation. UCIe provides the standardized interconnect fabric that makes chiplet

integration feasible, while virtual component modelling provides the visibility needed

to manage this complexity.

Through virtual models, architects can evaluate how different chiplet combinations

behave under real automotive workloads, analyze cross-chiplet dependencies, and

validate that performance and safety requirements are met. This approach

significantly reduces integration risk and shortens development cycles.

Commercial Tools for UCIe Virtual Modelling

Several commercial tools support UCIe-based system modelling across different

abstraction levels. Virtual prototyping platforms such as Synopsys Virtualizer and

Cadence Helium, Virtual System Platform enable early software development and

system validation using SystemC and TLM-based models. Emulation and

acceleration platforms such as ZeBu, Veloce, and Palladium are used when higher

accuracy or hybrid RTL-level validation is required.

These tools provide capabilities such as performance profiling, traffic analysis, debug

visibility, and integration with software stacks, all of which are essential for

automotive-grade validation.

Middleware Functions in Virtual Modelling

Middleware plays a critical role in connecting UCIe virtual components with software

and test environments. It abstracts low-level protocol details, manages

synchronization, provides transaction routing, and supports trace and metrics

collection. In automotive systems, middleware often includes safety monitoring

hooks and fault injection capabilities to support functional safety validation.

Well-designed middleware ensures that virtual models remain reusable, scalable,

and interoperable across tools and vendors.

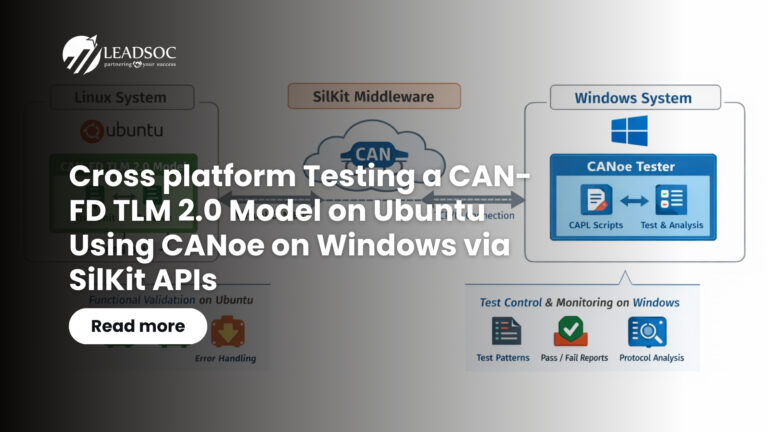

SILkit in UCIe-Based Virtual Integration

SILkit, originally developed for automotive system simulation, enables Software-in-

the-Loop integration of distributed virtual components. When applied to UCIe

modelling, SILkit allows multiple chiplet models, software stacks, and test scenarios

to be orchestrated in a coordinated simulation environment.

This approach is particularly useful for automotive use cases where system behavior

must be validated across ECUs, communication networks, and software layers.

SILkit supports realistic scenario execution, timing coordination, and interaction

between virtual hardware and application software.

TLM Sockets for Interfacing with Third-Party Tools

Transaction-Level Modeling using SystemC TLM 2.0 sockets is widely adopted for

integrating UCIe virtual components with third-party IP models, software frameworks,

and verification environments. TLM sockets enable high-speed simulation by

abstracting cycle-level details while preserving transaction semantics.

In automotive virtual platforms, TLM-based integration allows seamless co-

simulation between UCIe models, processor models, memory subsystems, and

external toolchains, supporting early software bring-up and system-level validation.

Skill Set Required for UCIe Modelling Roles

Engineers working in UCIe virtual component modelling require a strong foundation

in SystemC and TLM, along with a solid understanding of SoC and chiplet

architectures. Knowledge of interconnect protocols such as UCIe, PCIe, and CXL is

essential, as is familiarity with automotive system requirements and functional safety

concepts.

Equally important are skills in simulation tools, performance analysis, debugging

complex distributed systems, and collaborating across hardware and software

teams. These competencies enable engineers to bridge the gap between

architectural intent and system-level behavior.

Virtual component modelling of UCIe cores is a key enabler for next-generation

automotive SoCs built on chiplet architectures. By combining layered protocol

understanding, flit-based communication models, commercial virtual platforms,

middleware, SILkit, and TLM-based integration, automotive designers can de-risk

complex systems early and accelerate time to market.

At LeadSOC, we leverage deep expertise in interconnect protocols, virtual

prototyping, and automotive-grade system modeling to help customers build

scalable, safe, and future-ready semiconductor platforms.

With deep expertise in system modeling and virtual prototyping, LeadSOC

enables customers to design robust, future-ready silicon platforms for automotive,

industrial, and AI-driven applications. To explore more on deep technology SOCs,

Subscribe to the LeadSOC Blog for more System Modeling, VLSI, SoC

design, and semiconductor engineering insights.

Visit our website to explore our services, case studies, and technology

capabilities.

Smart minds are always welcome at LeadSOC follow our hiring posts on

LinkedIn and apply through our hiring portal and build the future of

SoCs with us.

RTL vs Gate Level Simulation — What’s the Difference?

VLSI Design Flow: A Complete Step-by-Step Guide

VLSI Design Services: Your Complete Guide to Choosing the Right Semiconductor Design Partner

Simulation in VLSI Design: Concepts, Types of Simulators, and the Role of Verilator

Complete VLSI Companies List 2025: Product-Based, Service-Based & Startup

Top 50 VLSI Companies in the World You Should Know in 2026

Agentic AI Assistant for Pregnancy and Mother Care: A Case Study in User-Centric Intelligence

Work-Life Balance at Leadsoc Technologies: Building Sustainable Careers, Not Burnout

Cross platform Testing a CAN-FD TLM 2.0 Model on Ubuntu Using CANoe on Windows via SilKit APIs

CAN FD and CAN XL Controllers in Next-Generation Automotive Networks

- 1

- 2